A perpetual calendar is an annual calendar that records a certain period of time. Its name is only a symbol, indicating a large time span. Because its function is very common and it is extremely convenient for people to use it, it is widely used in watches, ephemerides publications, electronic products, computer software and mobile phone applications.

Compared with traditional timekeeping tools such as clock calendars, digital calendars have many advantages such as high accuracy, low cost, stable operation, and diverse functions. Therefore, many designers at home and abroad have carried out related design and development. Among them, based on the FPGA development in addition to the design is simple, low development costs, circuit simplicity, etc., but also has the advantage of flexible design features. Only need to do a simple modification in the software to add different functions, such as alarm clock, yin and yang calendar control and so on.

In FPGA design, digital calendars are small-scale integrated circuits. In principle, it is a typical digital circuit, including combinational logic circuits and sequential circuits. The specific functional requirements in this case are as follows:

1. After the upper board is reset, counting is started from January 1 of the first year. To facilitate board debugging, the time of day is reduced to 1 second.

2. Press the key to set the calendar, press the key 0 to enter the setting state, press the key 0 again to exit the setting state;

3. Button 1 is used to select the year, month, and day of each bit;

4. Press button 2 to set the count in the setting state. Each press of the digital tube displays the number plus 1;

5. 365 days in the week (52 weeks + 1 day) and 366 days in the following year (52 weeks + 2 days), of which 28 days in February and 29 days in February of the following year.

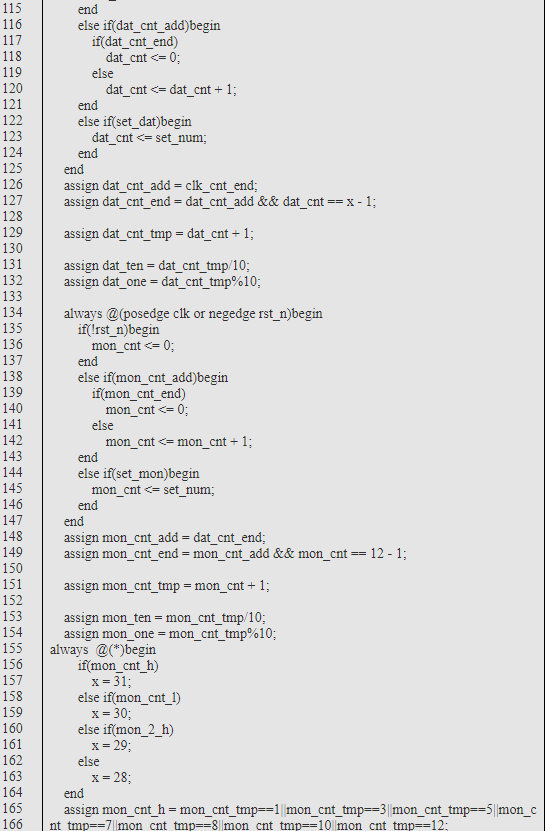

6. Jubilee: A glimpse every 400 years, or every 4 years and not a hundred years. A year that is divisible by 400, or divisible by 100 but divisible by 4 is a leap year.

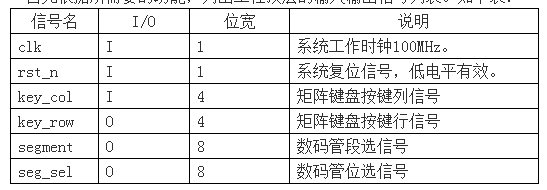

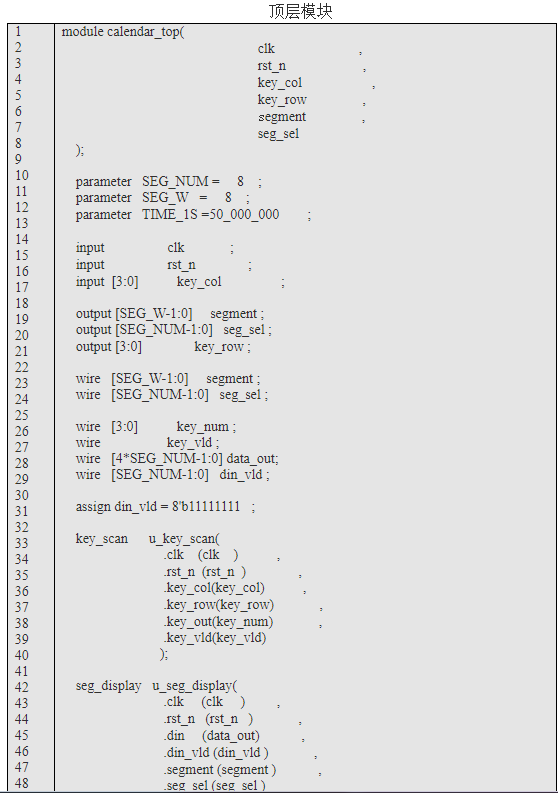

2 design ideasFirst, according to the required function, list the input and output signals of the top layer of the project. The following table:

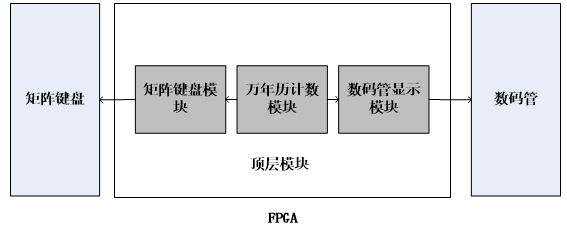

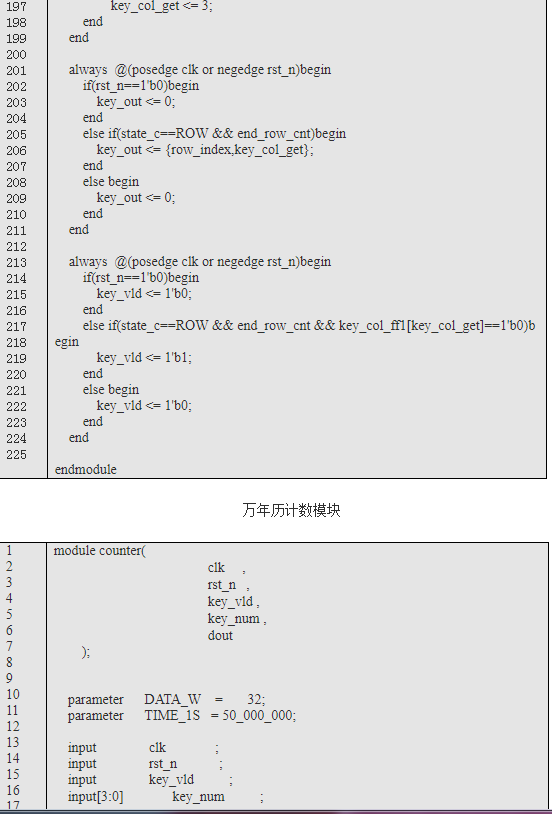

We can divide the project into three modules, which are perpetual calendar counting module, button module, and digital tube display module.

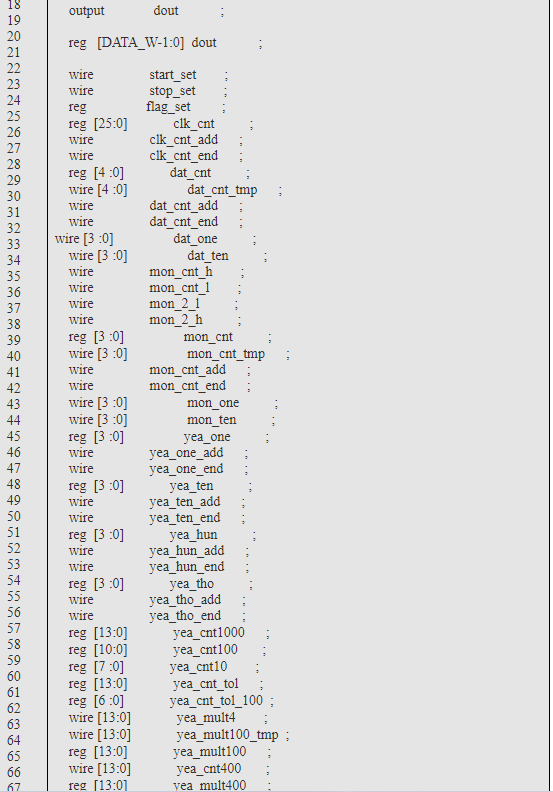

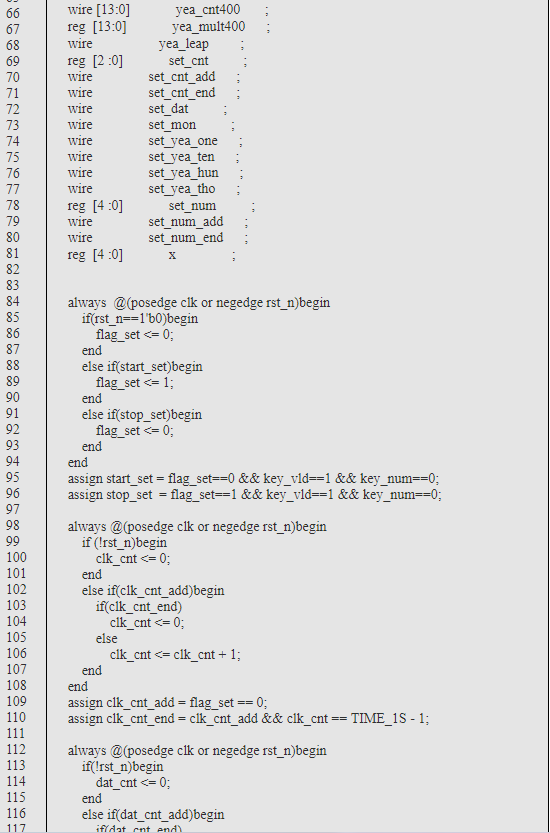

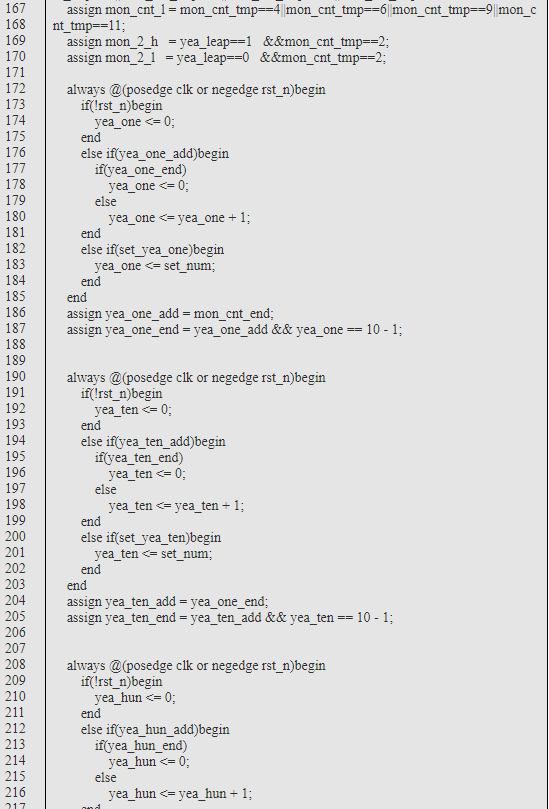

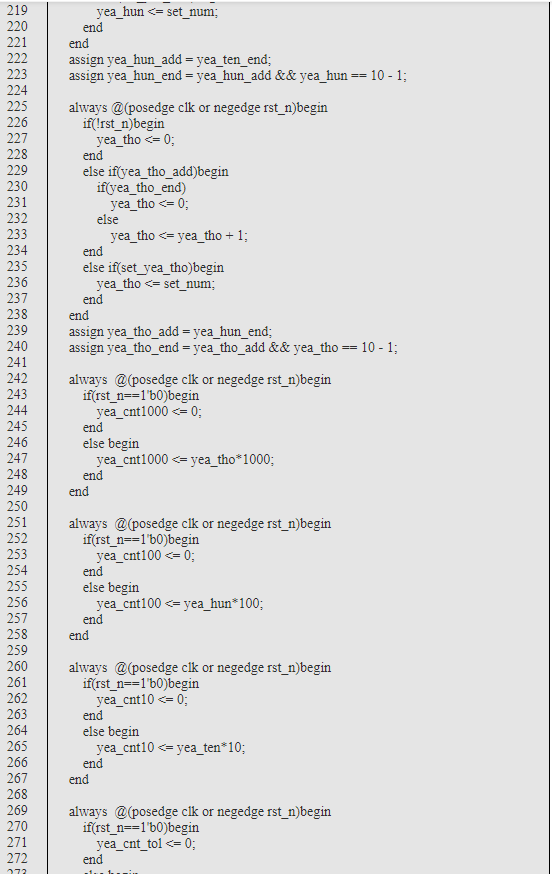

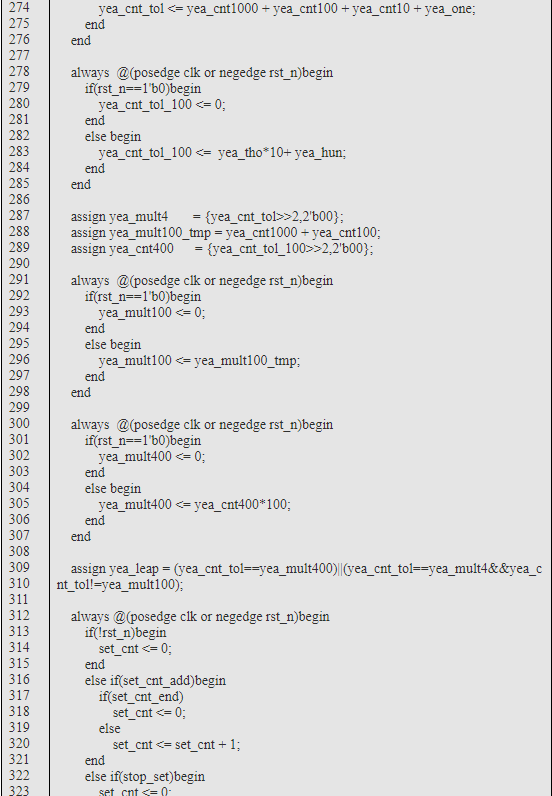

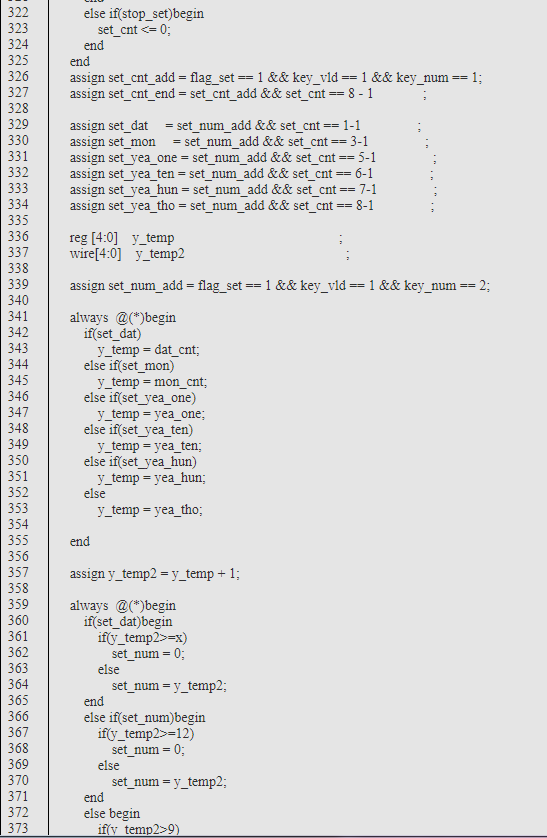

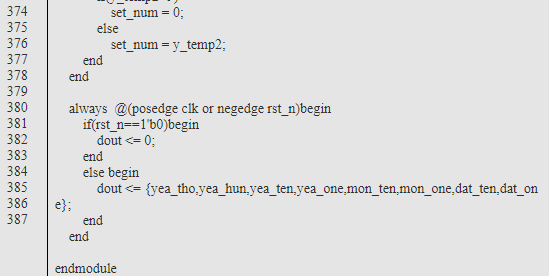

1. Counting module - to achieve the perpetual calendar counting function, for the convenience of viewing, the day time is set to 1 second; daily counters dat_cnt, month counters mon_cnt_h, mon_cnt_1, mon_2_h, mon_2_1 are respectively the month of the month and the year of the year. The counters, the year counters yea_one, yea_ten, yea_hun, yea_tho are each ten thousand bits of the year, and the year is obtained by yea_cnt_tol << yea_cnt1000 + yea_cnt100 + yea_cnt10 + yea_one. This module also automatically calculates whether the current year is a flat year.

The signal list is as follows:

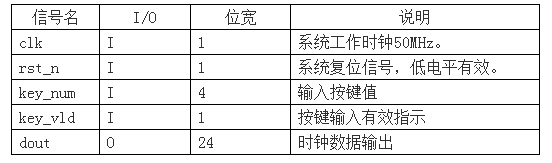

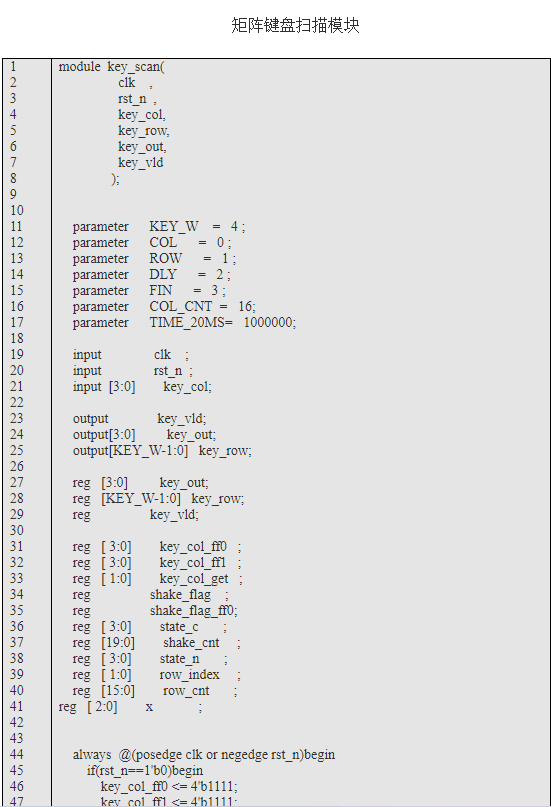

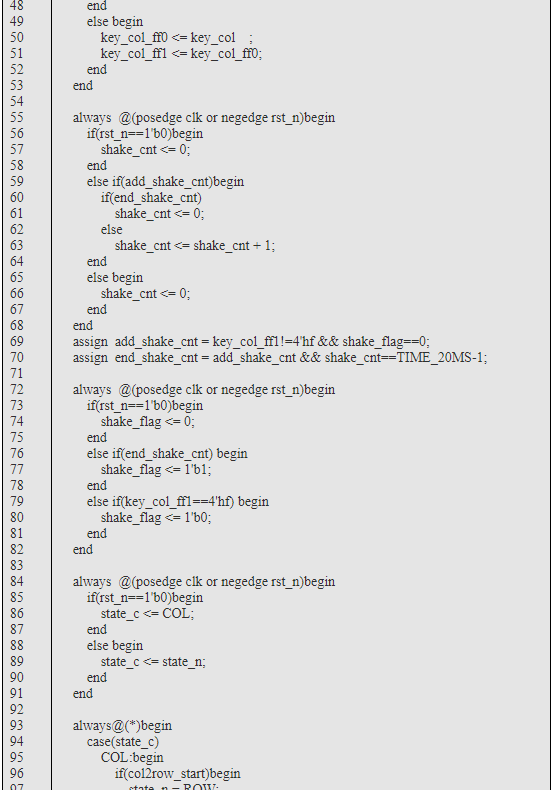

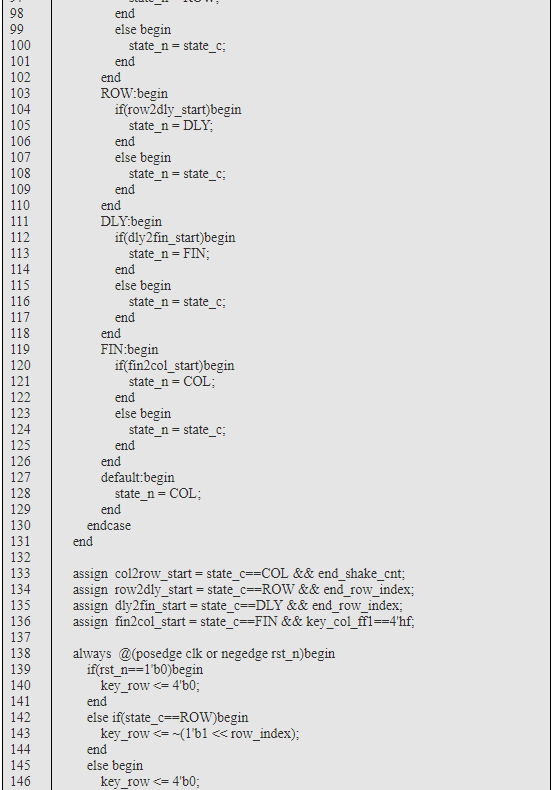

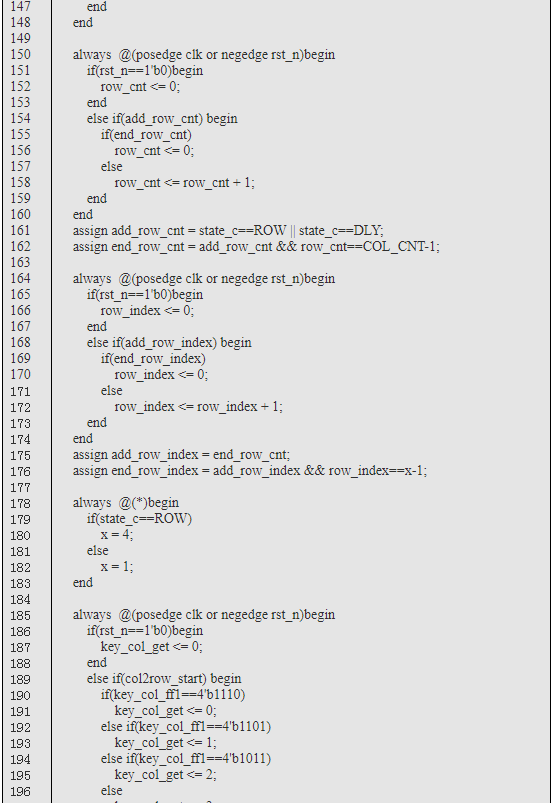

2. Button module - 4x4 matrix keyboard, to achieve a matrix keyboard scan and use the button to eliminate jitter function.

The signal list is as follows:

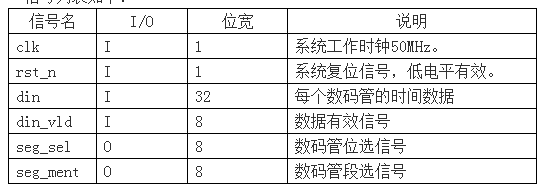

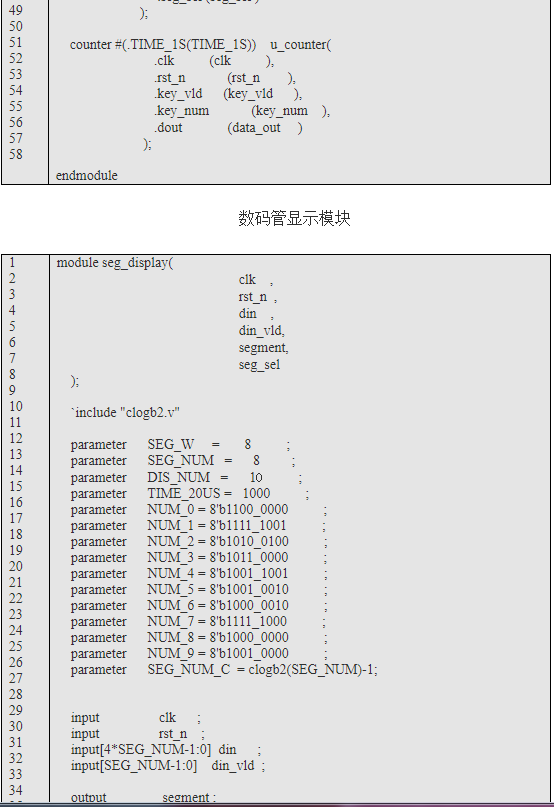

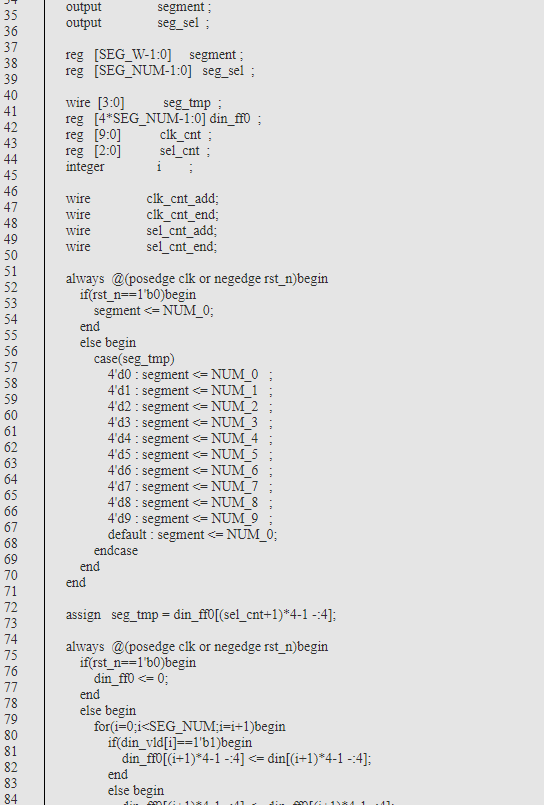

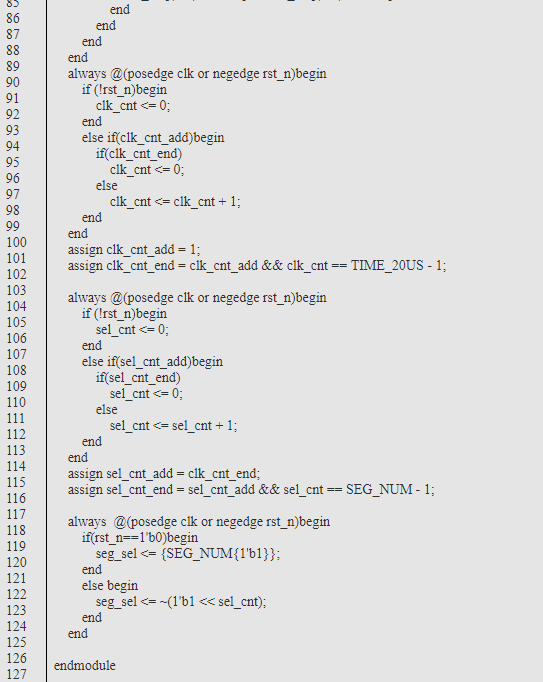

3. Digital tube module - to achieve the year, month, day information displayed on the digital tube.

The signal list is as follows:

The Smart Screen Protector Cutting Machine can help stores reduce the inventory of Screen Protectors. It is mainly used to cut Screen Protectors such as Mobile Phone Screen Protectors, Watch Screen Protectors, Tablet Screen Protectors, Pad Screen Protectors, and personalized fashion Back Films. It is very suitable for personal business or shop drainage.

Universal Screen Protector Cutting Machine has 20000+ cloud data of different specifications and models, adopts massive cloud database, and all data is updated synchronously in the state of networking. You'll have a full range of screen protector models on one machine and cut any Screen Protector model as needed without having to stock up on Screen Protectors for various phone models. No more losing customers due to missing models.

Screen Protector Cutting Machine,Protective Film Cutting Machine,Back Sticker Cutting Machine,Phone Sticker Cutting Machine, Film Cutting Machine

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.jjthydrogelmachine.com