Many industrial control systems maintain precise adjustment of certain key parameters (electrical, mechanical, thermal, or hydraulic) through the use of sophisticated high-order control loops. In this era of rapid technological development, control system designers are facing unprecedented challenges in achieving their design goals. The system must be faster, more accurate, and more flexible than ever, while integrating more functions into a shrinking enclosure and consuming less power. Therefore, people need new solutions that can not only improve the performance level of existing designs, but also realize new functions. The core of many industrial control systems is an analog-to-digital converter (ADC). In systems such as power grid monitors, optical network switches, and production robot systems, ADCs play a very important role, converting key signals from analog to digital for digital signal processing. This analog-to-digital conversion must be done more and more with high resolution, high speed and low power consumption.

Improve your control system

Many control system designers rely on successive approximation register (SAR) ADCs to accurately digitize their critical analog signals. Fundamentally speaking, the characteristic of SAR ADC is that it can obtain the precise “instant state†in the time domain of the input signal and complete the analog-to-digital conversion in a single clock cycle. Because the input is sampled at a precise instant in the time domain and results can be obtained immediately within the same clock cycle, SAR ADCs are good at asynchronous "start-and-go operaTIon" operations. SAR ADCs can produce conversion results quickly and accurately, and there is no cycle delay even after a long idle period (so-called "one-shot" operation), making it an ideal choice for control system applications. Other types of ADCs (such as delta-sigma ADCs and pipelined ADCs) require multiple clock cycles to complete a single conversion, making them more difficult to use in control systems.

Since many applications require multiple control loops to operate simultaneously in a given system, the board area and power dissipation of the ADC are also important considerations. For example, for new optical network switches, channel density is a key selling point. These systems often use small low-power SAR ADCs to monitor and control the output power level of each optical channel. Therefore, in order to achieve a faster and more responsive control system, a high-resolution, high-speed, and low-power SAR ADC with single trigger accuracy is required.

Breakthrough performance

Linear Technology recently launched a new series of high-performance SAR ADCs designed to solve the aforementioned major problems. The LTC2379-18 and LTC2380-16 are the first commercially available products in a pin- and software-compatible SAR ADC series, with 101dB SNR (at 18 bits) and 96dB SNR (at 16 bits) with sampling rates from 250ksps to 2Msps. This performance is achieved while maintaining low operating power consumption, ranging from 3.75mW (at 250ksps) to 19mW (at 2Msps). Each device is available in a small MSOP-16 package or DFN-16 package. Table 1 lists the summary information of the new ADC series.

In order to take care of system designers who are responsible for evaluating and selecting ADCs, this article will discuss several important SAR ADC performance indicators related to their use in control systems to reduce the involvement of selecting the best ADC in control systems and other demanding applications Uncertainty.

Control system requirements

The high-resolution control system needs to use a high-resolution ADC to perform more precise digital processing on the input signal, which is very natural. The ADC must complete the conversion operation while minimizing the signal link noise. As we all know, ADC noise can be reduced by averaging the results of multiple conversions. The cost of this approach is that the effective conversion rate is reduced. The low-noise ADC not only provides accuracy and resolution, but also achieves a higher operating speed, thereby improving the response time of the control system. Designers must make trade-offs between resolution, speed, noise, and power requirements to achieve the overall goals of the system.

Noise System designers can evaluate the noise performance of a SAR ADC through two very different specifications. For systems that digitize signals with dynamic AC components, signal-to-noise ratio (SNR) is an instructive indicator. The higher the SNR, the greater the dynamic range between the ADC's fundamental signal and the noise layer. A low-noise ADC can provide a larger noise margin for the signal processing link, thus helping to relax system design constraints. Figure 1 shows the FFT curve of LTC2379-18. This device is an 18-bit, 1.6Msps SAR ADC with 101dB SNR. The extremely low noise layer of this high-speed SAR ADC provides unprecedented flexibility and ease of use in the design of industrial control systems.

For systems that are primarily responsible for regulating static DC signals, switching noise is an instructive specification. When the ADC input is held at a fixed level, the conversion noise is a direct measure of the code scattered on the ADC output. The lower the conversion noise, the more stable the ADC output, which can provide accurate measurements with less averaging. Figure 2 shows the conversion noise characteristics of the LTC2380-16, which is a 16-bit, 2Msps SAR ADC. When the conversion noise is less than 0.2LSB, there is no need to use averaging to reduce the uncertainty in the ADC output, thereby realizing true one-shot operation at high speed.

Speed ​​Because many factors that affect transistor-level design conflict with each other, designers often need to make trade-offs between ADC noise, speed, and power consumption. Compared to higher-speed ADCs, lower-speed ADCs tend to maintain lower operating noise. When comparing the relative speeds of different SAR ADCs, it is helpful to not only look at the nominal sampling rate in the product specifications, but also understand the guaranteed conversion time. This is especially necessary for serial devices that use a serial peripheral interface (SPI) bus to transfer the conversion results to a digital processor. The nominal throughput of serial ADCs can be increased, but at the cost of users having to use a higher-speed digital interface. Figure 3 shows a typical timing diagram of a delay-free SAR ADC with a serial interface. The total cycle time is composed of conversion time and acquisition time. Usually, serial data transmission takes place during the acquisition time window. For a given cycle time, a shorter converter time can provide a longer serial data transmission window, thereby reducing the required digital interface speed. Of course, the shorter conversion time also minimizes the delay from the sampling time to obtaining the digital result, which is an important consideration for the control system. Therefore, when comparing the relative speed of different serial ADCs, it is recommended that you pay close attention to the conversion time specifications.

Reliability In addition to performance specifications, many industrial control system designers must maintain high reliability standards for their products, and therefore require that the selected main components (including ADCs) have high reliability. For applications that value quality awareness, it is crucial to select the ADC with the minimum and maximum specification limits for all major performance specifications (eg, INL, DNL, ​​SNR, and THD). These specifications must be guaranteed over the entire operating temperature range of the application. If the main parameters mentioned above are only guaranteed at room temperature or within a narrow temperature range, then the user must be especially careful. If the design lacks ruggedness, the specifications of the internal unit components of the high-resolution SAR ADC will vary greatly with temperature. If the selected ADC does not provide guaranteed specification limits over a wide temperature range, it will bring unnecessary risks to the design.

High efficiency solution

Reducing power consumption is an important goal of many modern designs, including control systems. In addition to the obvious advantages of low power consumption, many systems are also limited by thermal considerations and the ability to remove excess heat from within a narrow enclosure. This is especially true for systems that need to integrate dozens or hundreds of channels into a high-density circuit board (PCB). Therefore, power consumption and integration density are two important performance metrics when choosing a SAR ADC.

Traditional high-resolution SAR ADC signal links often require ADC driver amplifiers powered by separate power supplies. For a signal swing of 0V to 5V, a ± 6V power rail is not uncommon. In driver amplifiers and even so-called rail-to-rail output amplifiers, negative power supplies are needed to maintain good distortion performance, because the output transistor must maintain a minimum voltage across it to maintain high linearity. This added negative power rail not only consumes power, but its generation and wiring on the entire PCB are very troublesome.

Faced with these constraints, power-conscious designs generally eliminate the need for additional driver amplifier negative power supply by attenuating the input signal and using only a small portion of the full-scale input signal range. This method reduces the output swing requirements of the ADC driver amplifier. However, because only a small part of the available codes and input signal range are used, the effective resolution of the control system is reduced.

Digital gain compression

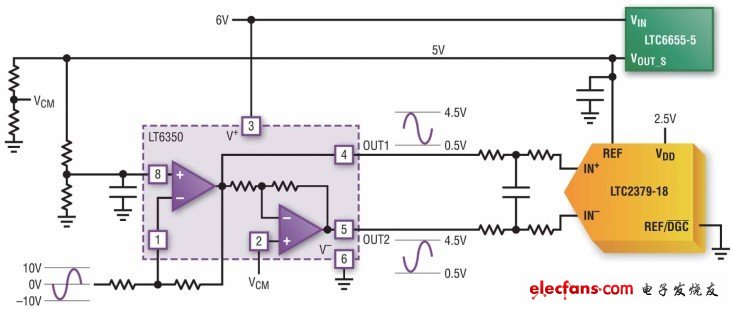

To overcome the above basic limitations, the LTC2379-18 and LTC2380-16 series are equipped with a unique digital gain compression (DGC) function that eliminates the negative power supply of the driver amplifier and maintains the full resolution of the ADC. When enabled, the ADC will perform a digital scaling function-convert the zero-scale code from 0V to 0.1 * VREF, and the full-scale code from VREF to 0.9 * VREF. For a typical reference voltage of 5V, the full-scale input range is now 0.5V to 4.5V, which provides sufficient reserve space for powering the drive amplifier from a single 6V power supply. As shown in Figure 4, the DGC function allows the ADC to generate all codes including zero and full scale (for example: for an 18-bit ADC, there are 218 = 262,144 codes in total), while reducing the output swing of the ADC driver amplifier. Request. Figure 5 shows a complete signal link. With the DGC function of LTC2379-18, this link can use a single 6V power supply to digitize an industrial ± 10V true bipolar signal into an 18-bit code at a sampling rate of 1.6Msps. This circuit was implemented in the demonstration system of LTC2379-18 and achieved 99dB SNR and over 100dB THD. Because it eliminates the negative power supply of the driver amplifier and utilizes the full range and resolution of the ADC, it provides a unique solution suitable for new industrial control systems.

in conclusion

In short, high-resolution, high-speed, and low-power SAR ADCs are very suitable for solving the problems of new industrial control systems. The recent improvements in speed, noise, and power consumption of these devices will result in innovative system designs that were previously impossible. Linear Technology ’s LTC2379-18 and LTC2380-16 are the first products in a pin- and software-compatible SAR ADC family with 101dB SNR (at 18 bits) and 96dB SNR (at 16 bits) at a sampling rate For 250ksps ~ 2Msps. Their ultra-low noise and low power consumption characteristics, coupled with the unique digital gain compression (DGC) function that enables the operation of single-supply driver amplifiers, make these new SAR ADC devices ideal for highly integrated control that requires optimal performance system design.

about the author:

â— Dr. Atsushi Kawamoto (Design Manager)

â— Dr. Jesper Steensgaard (Senior Design Engineer)

â— Dr. Heemin Yang (Senior Design Engineer)

Hongkong Onice Limited , https://www.ousibangvape.com