Abstract: Glitch is very common in FPGA design, and the appearance of glitch often leads to errors in system results. This paper deeply discusses the causes and conditions of glitch from the perspective of the principle structure of FPGA, summarizes a variety of different solutions, and analyzes the solution in depth with specific applications.

FPGA (F ield P rogrammable Gate A rray) is widely used in modern digital communication systems due to its large capacity, strong function and high reliability. Designing digital circuits using FPGAs has become one of the main design approaches in the field of digital circuit systems [1]. In the design of FPGAs, glitch is one of the design problems that have long plagued electronic design engineers, and is a major factor affecting the efficiency of engineers' design and the effectiveness and reliability of digital system design. Due to the delay caused by the signal being routed inside the FPGA and passing through the logic unit, the output of the combinational logic often produces small spikes, ie, glitch signals, at the instant of multiple signal changes, which is determined by the internal structural characteristics of the FPGA. Glitch is unavoidable in FPGA design, and sometimes any glitch can cause system errors, especially for spikes or pulse edge sensitive circuits. Therefore, overcoming and solving the glitch problem is especially important for modern digital system design. In this paper, the causes and conditions of glitch are discussed from the perspective of the principle structure of FPGA. On this basis, a variety of different elimination methods are summarized. At the end, the solution is deeply analyzed in combination with specific applications.

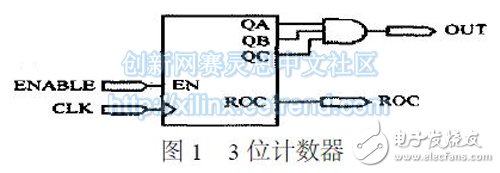

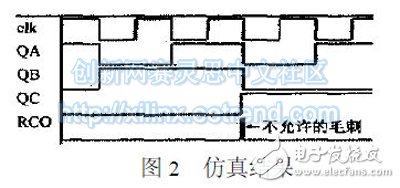

1 Causes of burrsThe cause of the glitch is analyzed in the example of Figure 1: Figure 1 is a 3-bit synchronous addition counter. When the enable is high, QA, QB, QC gradually change from 000 to 111 at the rising edge of each clock. After entering the all-one state, the carry output outputs a high level of half a clock pulse width, but from the simulation results in Fig. 2, it can be seen that the ROC has a sharp pulse, that is, a glitch, when the 011 changes to 100.

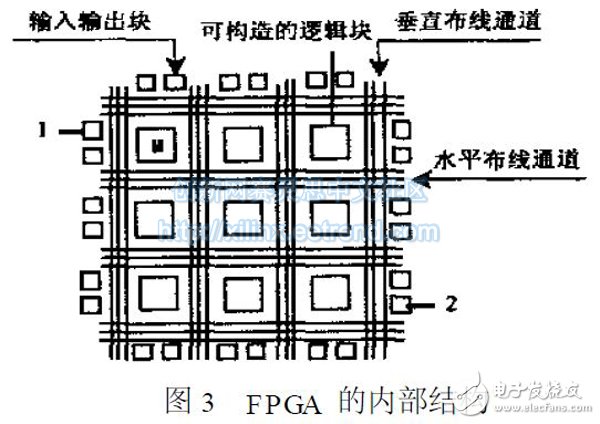

Take Xilinx's FPGA as an example to analyze its internal structure, as shown in Figure 3.

The FPGA chip is composed of three configurable units: a configurable input/output block (IOB), a Cinfigurable Logic Block (CLB), and a Programmable Interconnect Array (PIA). The IOB is located around the chip and provides a programmable interface between the internal logic array and the external chip package pins. It consists primarily of logic gates, flip-flops, and control units. The CLB constitutes the core array of the FPGA and can perform user-specified logic functions. Each CLB mainly consists of a combinational logic, several flip-flops, several multiple-choice circuits and control units. The PIA is located between the logic blocks inside the chip. , programmed to form a network of connections, used to interconnect the internal logic of the chip, and to pass information between them. As can be seen from Figure 3, for different inputs 1, 2, the trace to the logic block (M) may be different, which causes the delay of the input signal, assuming that 1, 2 change simultaneously, due to the existence of delay When there is a first arrival after reaching M (this phenomenon is called competition), there may be dangers (also called adventures) at the logical output, that is, glitch is generated. In the 011 state in the above example, it is assumed that QA and QB change from 1 to 0 at the same time, and QC advances from 2 ns from 0 to 1, producing a high level of 2 ns, which is the glitch. That is, in an FPGA design, the root cause of the glitch is the delay that occurs when the signal is routed inside the chip.

2 Conditions for burrsUse the same example to analyze the conditions under which burrs are produced. QA, QB, and QC flip at the same time on each rising edge of the clock. However, due to the delay, the wiring length of QA, QB, and QC to D flip-flops cannot be guaranteed. If QC is 2 ns ahead of QA and QB, this forms an all-one state of 2 ns, called "illusion all 1", which in turn causes the carry output to produce a sharp pulse. It is worth noting that when 3 is changed to 4, that is, 011 to 100, 2 of the 3 bits are flipped at the same time, that is, more than one signal changes at the same time. Due to the effect of the delay, the time at which multiple signals arrive at the end point is first and foremost, and competition is formed. The erroneous output produced by the competition is a glitch. Therefore, the condition of the glitch is that there are multiple signal inputs that change at the same time.

3 Ways to eliminate burrsKnowing the conditions of the burr, you can reduce the occurrence of burrs by changing the design and destroying the conditions. For example, using the Gray code counter to output only one bit transition at a time, instead of a normal binary counter, avoids the occurrence of glitch [3]. Circuitry can also be modified to eliminate the effects of burrs on the system. The following describes each method separately:

3, 1 using the redundancy methodThere are two ways to eliminate glitch with redundant terms: algebraic method and Karnaugh map method, both of which eliminate danger by adding redundant terms, except that the former is for function expressions and the latter is for truth tables. Taking the Karnaugh map as an example, if the two Carnot circles are tangent, the corresponding circuit may cause a danger. Therefore, modify the Karnaugh map and add a circle at the tangent of the two circles of Karnato to add extra items to eliminate the logic adventure. However, this method cannot be eliminated for the glitch generated by the counter type.

ZGAR AZ MC Disposable

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

Our products include disposable e-cigarettes, rechargeable e-cigarettes, rechargreable disposable vape pen, and various of flavors of cigarette cartridges. From 600puffs to 5000puffs, ZGAR bar Disposable offer high-tech R&D, E-cigarette improves battery capacity, We offer various of flavors and support customization. And printing designs can be customized. We have our own professional team and competitive quotations for any OEM or ODM works.

We supply OEM rechargeable disposable vape pen,OEM disposable electronic cigarette,ODM disposable vape pen,ODM disposable electronic cigarette,OEM/ODM vape pen e-cigarette,OEM/ODM atomizer device.

Disposable E-cigarette, ODM disposable electronic cigarette, vape pen atomizer , Device E-cig, OEM disposable electronic cigarette

ZGAR INTERNATIONAL(HK)CO., LIMITED , https://www.oemvape-pen.com